### **3V PCS LINEAR POWER AMPLIFIER**

### RoHS Compliant & Pb-Free Product

### **Typical Applications**

- 3V CDMA PCS Handsets

- 3V CDMA KPCS Handsets

- 3V TDMA/GAIT PCS Handsets

- 3V CDMA 2000 PCS Handsets

- Spread-Spectrum Systems

- Portable Battery-Powered Equipment

### **Product Description**

The RF2196 is a high-power, high-efficiency linear amplifier IC targeting 3V handheld systems. The device is manufactured on an advanced Gallium Arsenide process, and has been designed for use as the final RF amplifier in 3V CDMA and CDMA2000 handsets as well as other applications in the 1750MHz to 1910MHz band. The RF2196 has a low power mode to extend battery life under low output power conditions. The package is an ultra small 4mmx4mm, 16-pin QFN plastic package with backside ground.

### **Optimum Technology Matching® Applied**

- ☐ Si BJT ☐ GaAs MESFET☐ Si Bi-CMOS☐ SiGe HBT☐ Si CMOS☐ InGaP/HBT☐ GaN HEMT☐ SiGe Bi-CMOS☐

- 9 16 15 14 13 VPD1 2 12 VCC1 MODE 3 11 VCC1 VPD2 4 10 VCC 8 9 5 DOL OUT GND 2

**Functional Block Diagram**

胀

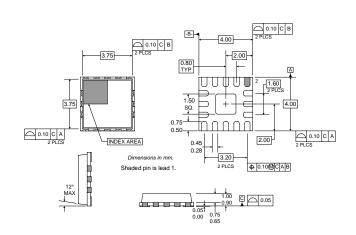

### Package Style: QFN, 16-Pin, 4x4

### **Features**

- Single 3V Supply

- 29dBm Linear Output Power

- 35% Linear Efficiency

- Low Power Mode (Up to 20dBm)

- 55mA Idle Current

### Ordering Information

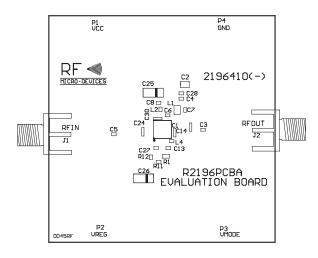

RF2196 3V PCS Linear Power Amplifier RF2196PCBA-41X Fully Assembled Evaluation Board

RF Micro Devices, Inc.

Tel (336) 664 1233

7628 Thorndike Road

Fax (336) 664 0454

Greensboro, NC 27409, USA

http://www.rfmd.com

## **RF2196**

### **Absolute Maximum Ratings**

| Parameter                                | Rating      | Unit     |  |  |  |

|------------------------------------------|-------------|----------|--|--|--|

| Supply Voltage (RF off)                  | +8.0        | $V_{DC}$ |  |  |  |

| Supply Voltage (P <sub>OUT</sub> ≤31dBm) | +5.2        | $V_{DC}$ |  |  |  |

| Mode Voltage (V <sub>MODE</sub> )        | +4.2        | $V_{DC}$ |  |  |  |

| Control Voltage (V <sub>REG</sub> )      | +3.0        | $V_{DC}$ |  |  |  |

| Input RF Power                           | +10         | dBm      |  |  |  |

| Operating Case Temperature               | -30 to +110 | °C       |  |  |  |

| Storage Temperature                      | -30 to +150 | ℃        |  |  |  |

RF Micro Devices believes the furnished information is correct and accurate at the time of this printing. RoHS marking based on EU Directive 2002/95/EC (at time of this printing). However, RF Micro Devices reserves the right to make changes to its products without notice. RF Micro Devices does not assume responsibility for the use of the described product(s).

| Parameter                                     | Specification |          | 1124 | O and Pittle on |                                                              |

|-----------------------------------------------|---------------|----------|------|-----------------|--------------------------------------------------------------|

|                                               | Min.          | Тур.     | Max. | Unit            | Condition                                                    |

| High Power State                              |               |          |      |                 | Case T=25°C, V <sub>CC</sub> =3.4V, V <sub>REG</sub> =2.85V, |

| (V <sub>MODE</sub> Low)                       |               |          |      |                 | V <sub>MODE</sub> =0V to 0.5V, Freq=1850MHz to               |

| ( MODE LOW)                                   |               |          |      |                 | 1910MHz (unless otherwise specified)                         |

| Frequency Range                               | 1850          |          | 1910 | MHz             |                                                              |

| Linear Gain                                   | 25            | 27       |      | dB              |                                                              |

| Second Harmonic                               |               | -50      |      | dBc             |                                                              |

| Third Harmonic                                |               | -63      |      | dBc             |                                                              |

| Maximum Linear Output Power (CDMA Modulation) | 29            |          |      | dBm             |                                                              |

| Total Linear Efficiency                       |               | 35       |      | %               | P <sub>OUT</sub> =29dBm                                      |

| Adjacent Channel Power Rejection              |               | -46      | -44  | dBc             | ACPR @ 1.25MHz                                               |

|                                               |               | -62      | -56  | dBc             | ACPR@2.25MHz                                                 |

| Input VSWR                                    |               | <2:1     |      |                 |                                                              |

| Output VSWR                                   |               |          | 10:1 |                 | No damage.                                                   |

|                                               |               |          | 6:1  |                 | No oscillations. >-70dBc                                     |

| Noise Power                                   |               | -141     |      | dBm/Hz          | At 80MHz offset.                                             |

| Low Power State                               |               |          |      |                 | Case T=25°C, V <sub>CC</sub> =3.4V, V <sub>REG</sub> =2.85V, |

|                                               |               |          |      |                 | V <sub>MODE</sub> =2V to 3V, Freq=1850MHz to                 |

| (V <sub>MODE</sub> High)                      |               |          |      |                 | 1910MHz (unless otherwise specified)                         |

| Frequency Range                               | 1850          |          | 1910 | MHz             |                                                              |

| Linear Gain                                   | 16            | 20       |      | dB              |                                                              |

| Second Harmonic                               |               | -45      |      | dBc             |                                                              |

| Third Harmonic                                |               | -60      |      | dBc             |                                                              |

| Maximum Linear Output Power (CDMA Modulation) | 16            | 20       |      | dBm             |                                                              |

| Max I <sub>CC</sub>                           |               | 160      |      | mA              | P <sub>OUT</sub> =+16dBm (all currents included)             |

| Adjacent Channel Power Rejection              |               | <-50     | -46  | dBc             | ACPR @ 1.25MHz                                               |

|                                               |               | <-60     | -58  | dBc             | ACPR@2.25MHz                                                 |

| Input VSWR                                    |               | 2:1      |      |                 |                                                              |

| Output VSWR                                   |               | <u>-</u> | 10:1 |                 | No damage.                                                   |

|                                               |               |          | 6:1  |                 | No oscillations. >-70dBc                                     |

2-346 Rev A2 060918

| Davamatar                                                                         | Specification                 |            | 11        | Condition |                                                                                                                                                    |

|-----------------------------------------------------------------------------------|-------------------------------|------------|-----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                                         | Parameter Min. Typ. Max. Unit |            | Condition |           |                                                                                                                                                    |

| High Power State CDMA<br>2000 1x (V <sub>MODE</sub> LOW)                          |                               |            |           |           | Case T=25°C, V <sub>CC</sub> =3.4V, V <sub>REG</sub> =2.85V, V <sub>MODE</sub> =0 V to 0.5 V, Freq=1850MHz to 1910MHz (unless otherwise specified) |

| Frequency Range Linear Gain Pilot+DCCH 9600                                       | 1850                          | 27         | 1910      | MHz<br>dB |                                                                                                                                                    |

| Maximum Linear Output Power<br>(CDMA 2000 Modulation)                             | 26.5                          |            |           | dBm       | 2.5dB Backoff included in IS95D 5.4dB peak to average at CCDF of 1%                                                                                |

| Adjacent Channel Power Rejection                                                  |                               | -49        |           | dBc       | ACPR@1.25MHz                                                                                                                                       |

| Pilot+FCH 9600+SCH0 9600                                                          |                               | -61        |           | dBc       | ACPR @ 2.25MHz                                                                                                                                     |

| Maximum Linear Output Power<br>(CDMA 2000 Modulation)                             | 29                            |            |           | dBm       | 4.5dB peak to average at CCDF of 1%                                                                                                                |

| Adjacent Channel Power Rejection                                                  |                               | -46        |           | dBc       | ACPR@1.25MHz                                                                                                                                       |

|                                                                                   |                               | -63        |           | dBc       | ACPR @ 2.25MHz                                                                                                                                     |

| Low Power State CDMA<br>2000 1x (V <sub>MODE</sub> HIGH)                          |                               |            |           |           | Case T=25°C, V <sub>CC</sub> =3.4V, V <sub>REG</sub> =2.85V, V <sub>MODE</sub> =2V to 3V, Freq=1850MHz to 1910MHz                                  |

| Frequency Range Linear Gain Pilot+DCCH 9600                                       | 1850                          | 19         | 1910      | MHz<br>dB |                                                                                                                                                    |

| Maximum Linear Output Power (CDMA 2000 Modulation)                                | 16                            | 20         |           | dBm       | 5.4dB peak to average at CCDF of 1%                                                                                                                |

| Adjacent Channel Power Rejection                                                  |                               | -52        |           | dBc       | ACPR @ 1.25MHz                                                                                                                                     |

|                                                                                   |                               | -65        |           | dBc       | ACPR@2.25MHz                                                                                                                                       |

| Pilot+FCH 9600+SCHO 9600<br>Maximum Linear Output Power<br>(CDMA 2000 Modulation) | 16                            | 20         |           | dBm       | 4.5dB peak to average at CCDF of 1%                                                                                                                |

| Adjacent Channel Power Rejection                                                  |                               | -52        |           | dBc       | ACPR @ 1.25MHz                                                                                                                                     |

|                                                                                   |                               | -65        |           | dBc       | ACPR @ 2.25MHz                                                                                                                                     |

| DC Supply                                                                         |                               |            |           | .,        |                                                                                                                                                    |

| Supply Voltage Quiescent Current                                                  | 3.0                           | 3.4<br>185 | 4.2       | V<br>mΛ   | V -Low                                                                                                                                             |

| Quiescent Current                                                                 |                               | 55         |           | mA<br>mA  | $V_{MODE}$ =Low<br>$V_{MODE}$ =High                                                                                                                |

| V <sub>REG</sub> Current                                                          |                               | 5          | 10        | mA        | MODE-111911                                                                                                                                        |

| V <sub>MODE</sub> Current                                                         |                               |            | 1 10      | mA        |                                                                                                                                                    |

| Total Current (Power Down)                                                        |                               |            | 10        | μΑ        | V <sub>REG</sub> =Low                                                                                                                              |

| V <sub>REG</sub> "Low" Voltage                                                    | 0                             |            | 0.5       | V         | REG                                                                                                                                                |

| V <sub>REG</sub> "High" Voltage                                                   | 2.75                          | 2.85       | 2.95      | V         |                                                                                                                                                    |

| V <sub>MODE</sub> "Low" Voltage                                                   | 0                             |            | 0.5       | V         |                                                                                                                                                    |

| V <sub>MODE</sub> "High" Voltage                                                  | 2.0                           |            | 3.0       | V         |                                                                                                                                                    |

## RF2196

| Pin         | Function | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Interface Schematic               |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 1           | GND      | This pin is internally grounded to the die flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                   |

| 2           | VREG1    | Power Down control for first stage. Regulated voltage supply for amplifier bias. In Power Down mode, both $V_{REG}$ and $V_{MODE}$ need to be LOW (<0.5 V).                                                                                                                                                                                                                                                                                                                                                                             |                                   |

| 3           | MODE     | For nominal operation (High Gain Mode), V <sub>MODE</sub> is set LOW. When set HIGH, the driver and final are dynamically scaled to reduce the device size and as a result to reduce idle current.                                                                                                                                                                                                                                                                                                                                      |                                   |

| 4           | VREG2    | Power Down control for the second stage. Regulated voltage supply for amplifier bias. In Power Down mode, both $V_{REG}$ and $V_{MODE}$ need to be LOW (<0.5V).                                                                                                                                                                                                                                                                                                                                                                         |                                   |

| 5           | GND      | Connect to ground plane via 15nH inductor. DC return for the second stage bias circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   |

| 6           | NC       | This pin has no internal bonding; therefore, this pin can be connected to output pin 7, connected to the ground plane, or not connected. Slight tuning of the output match may be required due to stray capacitance of the pin.                                                                                                                                                                                                                                                                                                         |                                   |

| 7           | RF OUT   | RF output and power supply for final stage. This is the unmatched collector output of the second stage. A DC block is required following the matching components. The biasing may be provided via a parallel L-C set for resonance at the operating frequency of 1710MHz to 1910MHz. It is important to select an inductor with very low DC resistance with a 1 A current rating. Alternatively, shunt microstrip techniques are also applicable and provide very low DC resistance. Low frequency bypassing is required for stability. | RF OUT  From Bias  Network        |

| 8           | RF OUT   | Same as pin 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | See pin 7.                        |

| 9           | GND      | This pin is internally grounded to the die flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                   |

| 10          | VCC      | Supply for bias reference and control circuits. High frequency bypassing may be necessary.                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                   |

| 11          | VCC1     | Power supply for first stage and interstage match. Pins 11 and 12 should be connected by a common trace where the pins contact the printed circuit board.                                                                                                                                                                                                                                                                                                                                                                               |                                   |

| 12          | VCC1     | Same as pin 11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                   |

| 13          | NC       | It is recommended that these pins be connected to the ground plane for improved isolation between RF IN (pin 16) and the VCC1 pins (pins 11 and 12).                                                                                                                                                                                                                                                                                                                                                                                    |                                   |

| 14          | NC       | It is recommended that these pins be connected to the ground plane for improved isolation between RF IN (pin 16) and the VCC1 pins (pins 11 and 12).                                                                                                                                                                                                                                                                                                                                                                                    |                                   |

| 15          | NC       | It is recommended that these pins be connected to the ground plane for improved isolation between RF IN (pin 16) and the VCC1 pins (pins 11 and 12).                                                                                                                                                                                                                                                                                                                                                                                    |                                   |

| 16          | RF IN    | RF input. An external 15pF series capacitor is required as a DC block. In addition, the matching circuit shown is required to improve input VSWR.                                                                                                                                                                                                                                                                                                                                                                                       | RF IN O  3.6 pF  From Bias Stages |

| Pkg<br>Base | GND      | Ground connection. The backside of the package should be soldered to a top side ground pad which is connected to the ground plane with multiple vias. The pad should have a short thermal path to the ground plane.                                                                                                                                                                                                                                                                                                                     |                                   |

2-348 Rev A2 060918

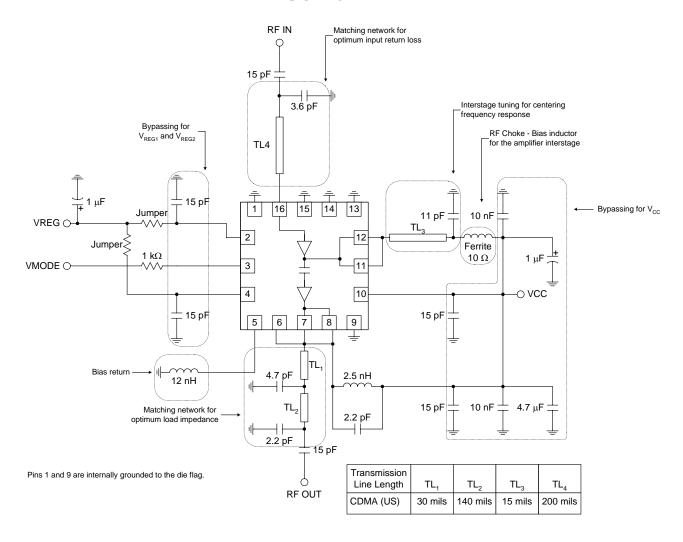

# Application Schematic US - CDMA

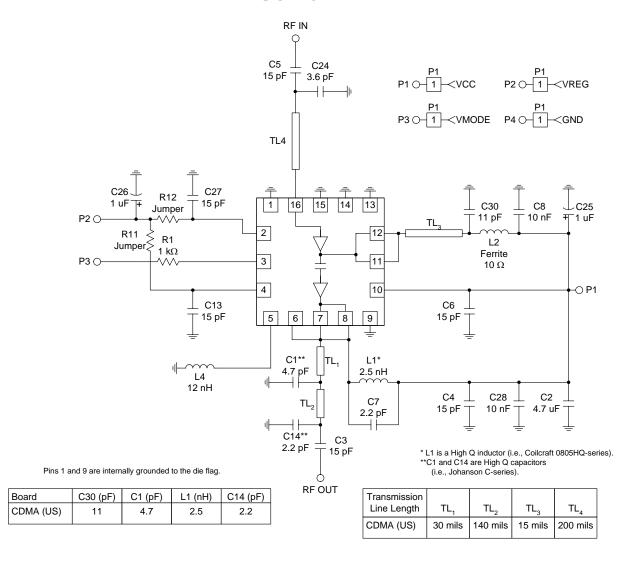

# **Evaluation Board Schematic US - CDMA**

2-350 Rev A2 060918

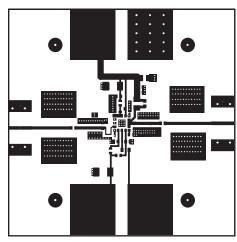

# Evaluation Board Layout Board Size 2.0" x 2.0"

Board Thickness 0.028"; Board Material FR-4; Multi-Layer; Ground Plane at 0.014"

### **PCB Design Requirements**

### **PCB Surface Finish**

The PCB surface finish used for RFMD's qualification process is electroless nickel, immersion gold. Typical thickness is 3µinch to 8µinch gold over 180µinch nickel.

### **PCB Land Pattern Recommendation**

PCB land patterns are based on IPC-SM-782 standards when possible. The pad pattern shown has been developed and tested for optimized assembly at RFMD; however, it may require some modifications to address company specific assembly processes. The PCB land pattern has been developed to accommodate lead and package tolerances.

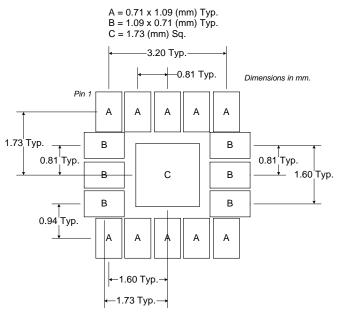

#### **PCB Metal Land Pattern**

Figure 1. PCB Metal Land Pattern (Top View)

2-352 Rev A2 060918

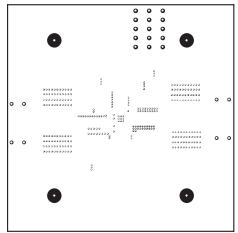

#### **PCB Solder Mask Pattern**

Liquid Photo-Imageable (LPI) solder mask is recommended. The solder mask footprint will match what is shown for the PCB Metal Land Pattern with a 3mil expansion to accommodate solder mask registration clearance around all pads. The center-grounding pad shall also have a solder mask clearance. Expansion of the pads to create solder mask clearance can be provided in the master data or requested from the PCB fabrication supplier.

Figure 2. PCB Solder Mask (Top View)

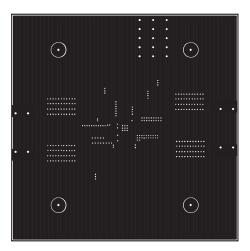

### Thermal Pad and Via Design

The PCB metal land pattern has been designed with a thermal pad that matches the exposed die paddle size on the bottom of the device.

Thermal vias are required in the PCB layout to effectively conduct heat away from the package. The via pattern has been designed to address thermal, power dissipation and electrical requirements of the device as well as accommodating routing strategies.

The via pattern used for the RFMD qualification is based on thru-hole vias with 0.203mm to 0.330mm finished hole size on a 0.5mm to 1.2mm grid pattern with 0.025mm plating on via walls. If micro vias are used in a design, it is suggested that the quantity of vias be increased by a 4:1 ratio to achieve similar results.

## RF2196

2-354 Rev A2 060918